How to Disable IOMMU on Nvidia Jetson Orin Nano Dev Board

Issue Overview

Users of the Nvidia Jetson Orin Nano Dev Board have reported difficulties in disabling the Input-Output Memory Management Unit (IOMMU) when attempting to connect a PCIe device, specifically a data acquisition card. The main symptoms include:

- Inability to disable IOMMU, which is necessary for certain hardware configurations.

- Confusion regarding the correct files and directories to modify in order to achieve this.

The issue typically arises during setup when users are configuring their boards for specific applications that require direct access to PCIe devices without IOMMU interference.

Relevant specifications include the Jetson Orin Nano hardware and its associated software environment, particularly the Linux for Tegra (L4T) operating system. The frequency of this issue appears to be consistent among users attempting similar configurations, impacting their ability to utilize external hardware effectively.

Possible Causes

Several potential causes for the inability to disable IOMMU have been identified:

-

Hardware Incompatibilities: Users may be unaware that different versions of the Jetson board (e.g., Orin Nano vs. others) may require different configurations.

-

Software Bugs or Conflicts: There may be existing bugs within the L4T software that affect IOMMU settings.

-

Configuration Errors: Users might be modifying incorrect files or parameters, leading to unsuccessful attempts at disabling IOMMU.

-

Driver Issues: Certain drivers may rely on IOMMU being enabled, causing conflicts when attempting to disable it.

-

User Errors or Misconfigurations: Incorrectly identifying the necessary files or directories can lead to confusion and failed attempts.

Troubleshooting Steps, Solutions & Fixes

To address the issue of disabling IOMMU on the Nvidia Jetson Orin Nano Dev Board, follow these comprehensive troubleshooting steps:

-

Identify the Correct Directory:

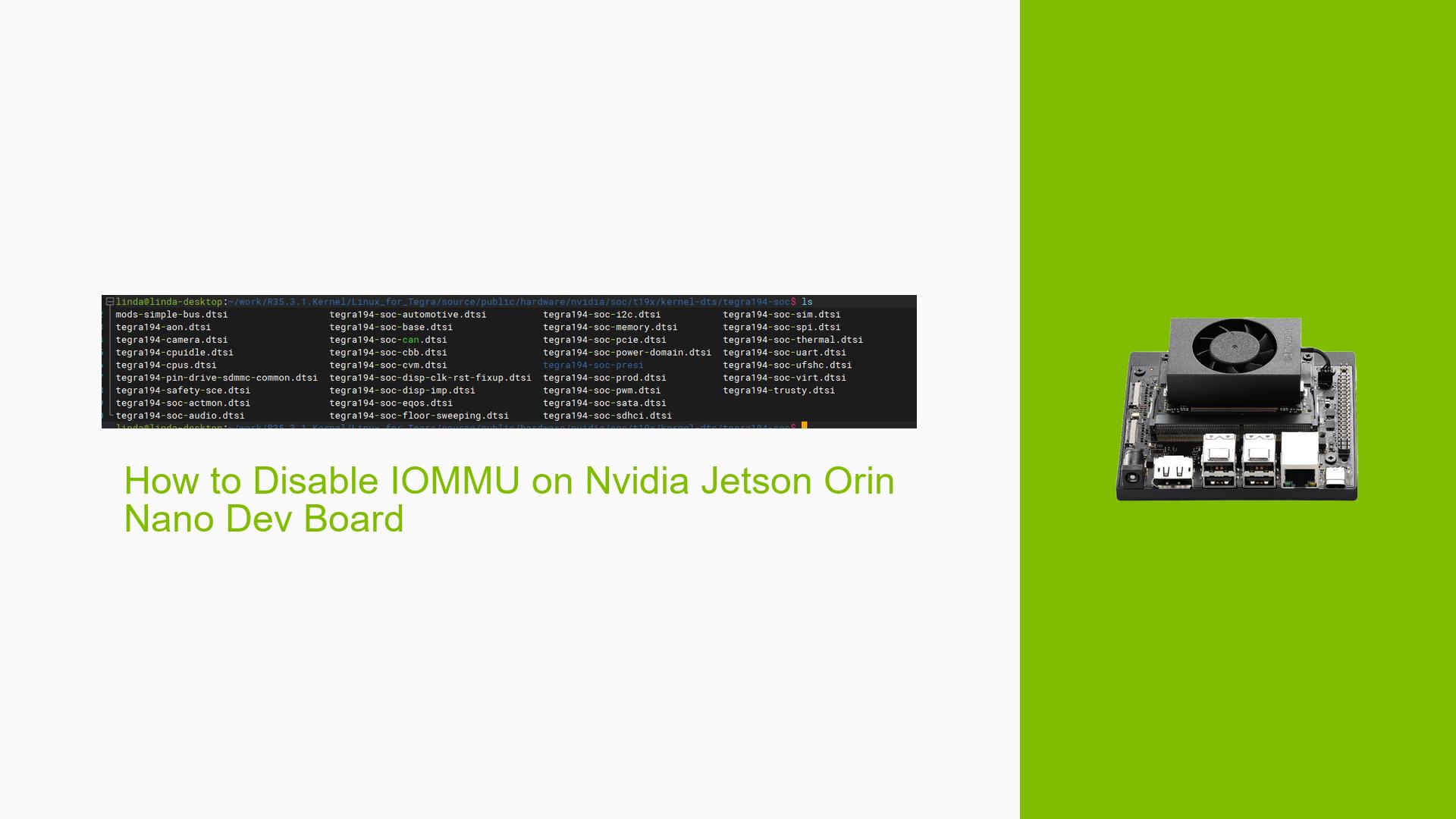

- Ensure you are looking in the right directory for your specific board version. For the Orin Nano, navigate to:

/Linux_for_Tegra/source/public/hardware/nvidia/soc/t23x/kernel-dts/

- Ensure you are looking in the right directory for your specific board version. For the Orin Nano, navigate to:

-

Locate Relevant Files:

- Within this directory, find files related to IOMMU settings. These may include device tree source files that define hardware configurations.

-

Modify Device Tree Files:

- Open the relevant device tree file associated with your PCIe controller.

- Disable IOMMU by modifying the appropriate properties. For example, you may need to set a property like

status = "disabled"for the SMMU node under your PCIe controller.

-

Recompile Device Tree Blob (DTB):

- After making changes, recompile the device tree blob using:

dtc -I dts -O dtb -o tegra194-p3668-all-p3509-0000.dtb <modified_file>.dts

- After making changes, recompile the device tree blob using:

-

Update Boot Configuration:

- Ensure that your bootloader is configured to use the updated DTB file. This may involve modifying boot parameters in

extlinux.conf.

- Ensure that your bootloader is configured to use the updated DTB file. This may involve modifying boot parameters in

-

Reboot System:

- After making these changes, reboot your Jetson board for them to take effect.

-

Testing Configuration:

- After rebooting, verify that IOMMU is disabled by checking system logs or using commands such as:

dmesg | grep IOMMU

- After rebooting, verify that IOMMU is disabled by checking system logs or using commands such as:

-

Documentation and Resources:

- Refer to Nvidia’s official documentation on device tree modifications and PCIe configurations for additional guidance.

- Keep an eye on forums for any updates or user-shared solutions regarding similar issues.

-

Best Practices:

- Always back up existing configuration files before making changes.

- Document any modifications made for future reference.

This structured approach should help users successfully disable IOMMU on their Nvidia Jetson Orin Nano Dev Boards and resolve related issues with PCIe device connectivity. Further investigation may be needed if problems persist after following these steps, particularly concerning software updates or deeper hardware compatibility issues.