Unable to Configure Pin 40 as CSI_E_D2_N on Nvidia Jetson Orin Nano Dev Board

Issue Overview

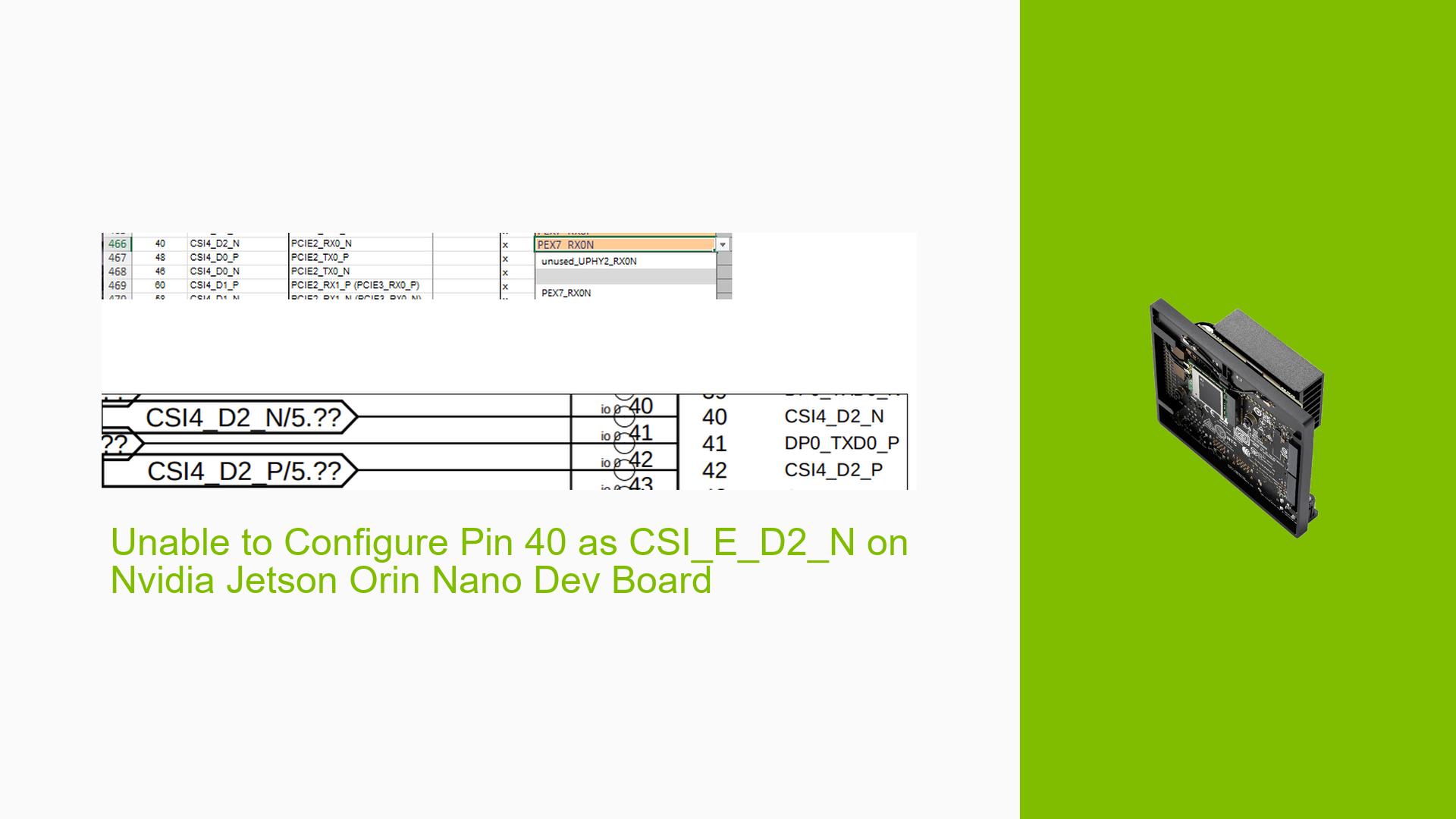

Users are experiencing difficulties when attempting to configure pin 40 on the Nvidia Jetson Orin Nano Dev Board. Specifically, the issue arises during the setup of a custom carrier board. According to the schematics, pin 40 should be set to CSI_4_D2_N (presumed to be equivalent to CSI_E_D2_N). However, users are unable to select this option in the dropdown menu, which only allows the selection of PEX7_RX0N. This limitation is preventing users from properly configuring the board for their specific use case, potentially impacting the functionality of camera interfaces or other components relying on the CSI (Camera Serial Interface) connection.

Possible Causes

-

Hardware Limitations: The Jetson Orin Nano Dev Board may have physical constraints that prevent certain pins from being configured for multiple functions.

-

Software Restrictions: The configuration software or firmware might be limiting the available options for pin 40, possibly due to design decisions or compatibility issues.

-

Documentation Discrepancy: There could be a mismatch between the schematics and the actual board capabilities, leading to confusion about the available pin configurations.

-

Outdated Software: The configuration tool or firmware might be outdated, lacking support for all possible pin configurations.

-

Design Guide Omission: The design guide documentation may not explicitly mention the ability to configure this pin for CSI use, indicating a potential limitation or oversight in the board’s design.

Troubleshooting Steps, Solutions & Fixes

-

Verify Documentation:

- Carefully review the Jetson Orin Nano Dev Board documentation, particularly the sections related to pin configurations and CSI interfaces.

- Look for any notes or exceptions regarding pin 40 and its available functions.

-

Check for Software Updates:

- Ensure you are using the latest version of the configuration software and board firmware.

- Visit the NVIDIA Developer website to download and install any available updates.

-

Consult NVIDIA Support:

- If the issue persists, reach out to NVIDIA’s technical support for clarification on pin 40’s capabilities.

- Provide them with your specific use case and the discrepancy between the schematics and available options.

-

Explore Alternative Pins:

- Investigate if other pins can be configured for the CSI_E_D2_N function.

- Review the pinout diagram to identify potential alternatives that may suit your needs.

-

Consider Hardware Workarounds:

- If pin 40 cannot be configured as desired, explore the possibility of using external multiplexers or signal routing on your custom carrier board to achieve the required functionality.

-

Review PCIe Requirements:

- Assess whether the PEX7_RX0N function is critical for your application.

- If PCIe functionality is not needed, you may be able to repurpose the pin in your custom design, bypassing the software configuration limitations.

-

Examine Design Guide Thoroughly:

- Pay close attention to the CSI section in the design guide document.

- If the CSI configuration for pin 40 is not mentioned, it likely indicates that this pin cannot be configured for CSI use through software means.

-

Community Forums:

- Engage with the NVIDIA Developer community forums to see if other users have encountered and resolved similar issues.

- Share your findings and collaborate on potential solutions or workarounds.

-

Custom Firmware Consideration:

- As a last resort, investigate the possibility of developing custom firmware that allows for the desired pin configuration.

- Note that this approach is complex and may void warranties or support agreements.

It’s worth mentioning that if the design guide document does not mention the ability to configure pin 40 for CSI use in the CSI section, it is likely that this configuration is not supported by the hardware or software. In such cases, you may need to redesign your custom carrier board to accommodate this limitation or explore alternative approaches to achieve your desired functionality.