Enabling UART0 on Nvidia Jetson Orin Nano Dev Board

Issue Overview

Users of the Nvidia Jetson Orin Nano Developer Kit have reported difficulties in enabling UART0 (UARTB) functionality, particularly when attempting to write to it. The symptoms include:

- Inability to see the expected UART device (

/dev/THS) after booting, despite modifying the device tree source (DTS) file. - The issue occurs during setup, specifically after flashing the device and attempting to enable UART0 in the DTS configuration.

- Users have noted that the UART0 appears to be disabled by default, leading to frustration when trying to access it for serial communication.

- The problem seems consistent across multiple attempts, impacting user experience significantly as it prevents effective communication with connected devices.

Relevant Specifications

- Jetson Model: Jetson Orin NX Engineering Reference Developer Kit

- Jetpack Version: 6.0 [L4T 36.3.0]

- Part Number: 699-13767-0005-300 M.1

- SoC: tegra234

Possible Causes

Several potential causes for the UART0 issue have been identified:

- Hardware Incompatibility: Users may be using custom carrier boards that do not support UART0.

- Software Bugs: There may be bugs in the Jetpack version or in the DTS files that prevent proper initialization of UART devices.

- Configuration Errors: Incorrect modifications to the DTS file may lead to UART0 not being recognized.

- Driver Issues: Missing or outdated drivers can cause hardware components not to function as expected.

- Environmental Factors: Power supply issues or thermal conditions could impact device performance.

- User Misconfiguration: Incorrect settings in the

extlinux.conffile or failure to include necessary entries can lead to problems.

Troubleshooting Steps, Solutions & Fixes

To resolve the issue with UART0 on the Jetson Orin Nano, follow these steps:

-

Verify Device Tree Configuration:

- Ensure that you have correctly modified the DTS file located at

/boot/dtb/tegra234-p3768-0000+p3767-0005-nv.dts. - Check that you have added the necessary entries for UART0:

serial3 = "/bus@0/serial@3110000"; uartb = "/bus@0/serial@3110000";

- Ensure that you have correctly modified the DTS file located at

-

Compile and Flash:

- After making changes, compile the DTS back into a DTB format and flash your device using:

sudo ./tools/kernel_flash/l4t_initrd_flash.sh --external-device nvme0n1p1 --erase-all -c tools/kernel_flash/flash_l4t_external.xml -p "-c bootloader/generic/cfg/flash_t234_qspi.xml" --showlogs --network usb0 jetson-orin-nano-devkit internal

- After making changes, compile the DTS back into a DTB format and flash your device using:

-

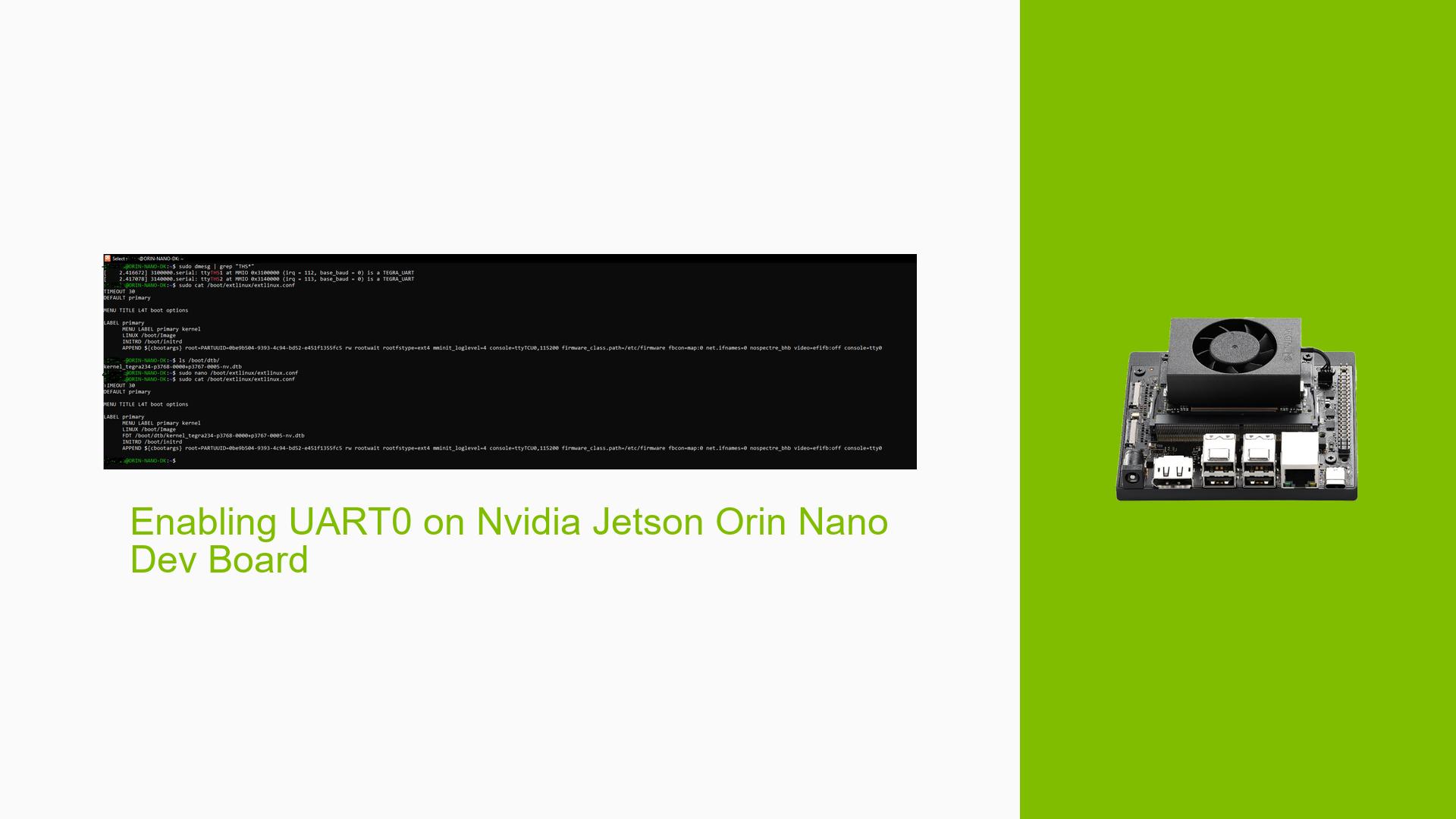

Check extlinux.conf:

- Confirm that your

extlinux.conffile contains a valid FDT entry pointing to your modified DTB:FDT /boot/dtb/tegra234-p3768-0000+p3767-0005-nv.dtb

- Confirm that your

-

Reboot and Verify Devices:

- Reboot your board and check if

/dev/THSappears using:ls /dev/ - If it does not appear, check for errors in the boot logs.

- Reboot your board and check if

-

Inspect Boot Logs:

- Use

dmesgor check/var/log/syslogfor any messages related to UART initialization.

- Use

-

Testing with Different Configurations:

- If issues persist, try testing with a different carrier board or Jetpack version (e.g., Jetpack 5.x) to rule out hardware or software incompatibilities.

-

Documentation and Support:

- Refer to Nvidia’s official documentation for additional guidance on device tree modifications and UART configurations.

- If problems continue, consider reaching out on Nvidia Developer Forums for community support.

Recommended Approach

If multiple users report success with specific configurations or methods, highlight those as best practices. For instance, ensuring all entries are correctly set in both DTS and extlinux.conf has led some users to successfully enable UART functionality.

Unresolved Aspects

Further investigation may be necessary regarding specific hardware configurations and compatibility issues with third-party carrier boards, as these can introduce additional complexities not covered in standard documentation.