Configuring SPI Interface on Nvidia Jetson Orin Nano Dev Board

Issue Overview

Users are experiencing issues with the SPI (Serial Peripheral Interface) configuration on the Nvidia Jetson Orin Nano Developer Kit, specifically when interfacing with a TPM (Trusted Platform Module) chip, the SLB9672. The primary symptom reported is that the MISO (Master In Slave Out) line is not behaving as expected; it remains high during data reading instead of low, which is the required idle state for proper operation. This issue arises during setup and testing phases, particularly when loading the tpm_tis_spi.ko module. Users have noted that despite configuring the device tree and pinmux settings, the desired low state is not achieved consistently. The frequency of this issue appears to be common among users configuring similar hardware setups.

Possible Causes

- Hardware Incompatibilities or Defects: The SPI interface may not be compatible with the specific TPM chip or there may be defects in the hardware connections.

- Software Bugs or Conflicts: There could be bugs in the drivers (

tpm_tis_core.koandtpm_tis_spi.ko) or conflicts arising from multiple applications accessing the SPI interface. - Configuration Errors: Incorrect settings in the device tree or pinmux configurations can lead to improper signal states.

- Driver Issues: Outdated or incompatible drivers might not support the required functionality for SPI communication.

- Environmental Factors: Issues such as power supply instability or temperature fluctuations could affect signal integrity.

- User Errors or Misconfigurations: Users may inadvertently misconfigure settings or fail to apply changes correctly after modifying configurations.

Troubleshooting Steps, Solutions & Fixes

-

Verify Device Tree Configuration:

- Ensure that the device tree entries for SPI0 and the TPM chip are correctly defined.

- Check that

statusfields are set to "okay" for both SPI0 and the TPM chip.

-

Check Pinmux Settings:

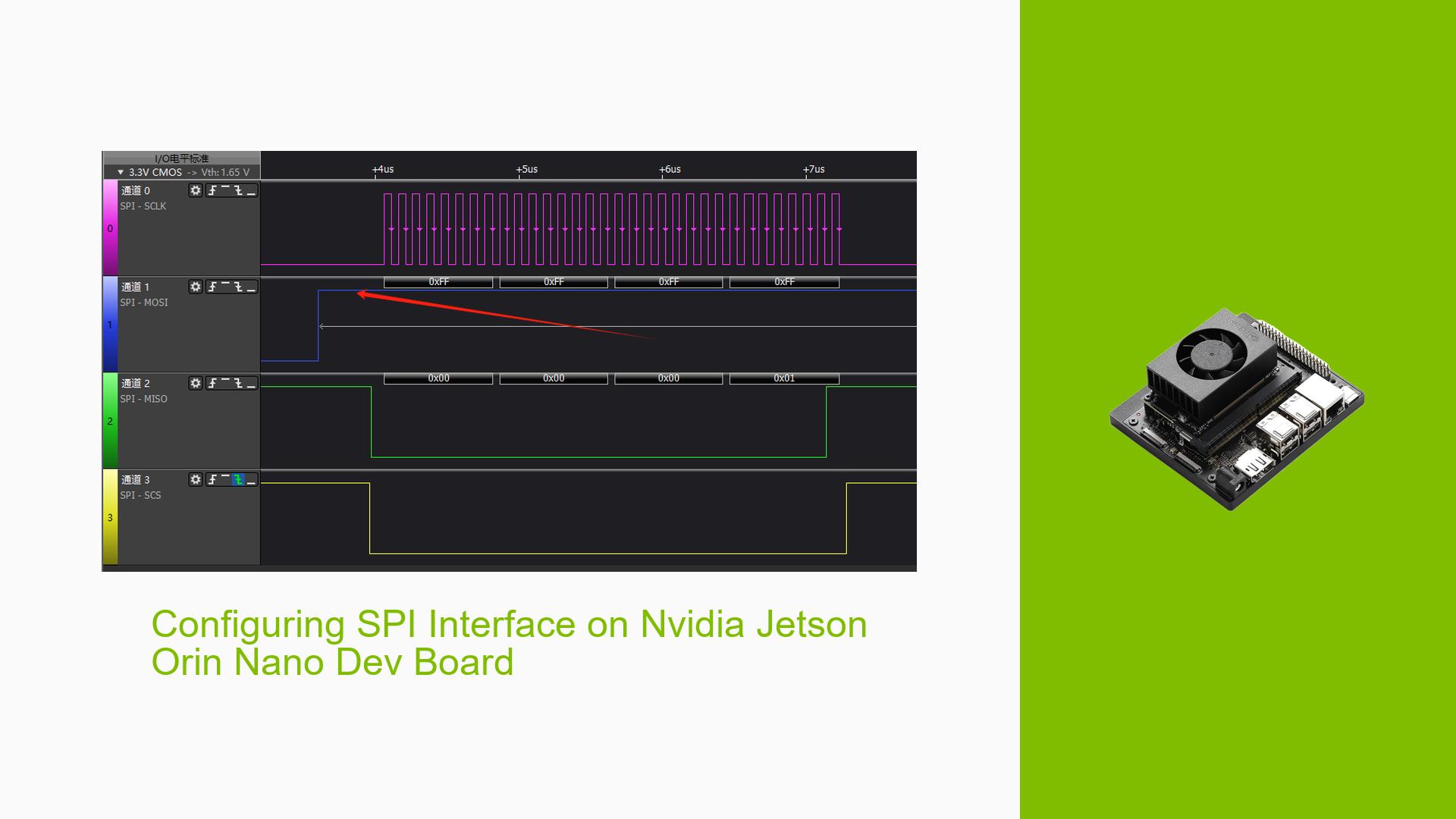

- Use a logic analyzer to verify pin states before and after configuration changes.

- Modify pinmux settings to ensure that MOSI is set to drive low at idle:

pinmux configuration: Drive 0 for MOSI

-

Run Diagnostic Commands:

- Execute the following command to check register values:

sudo busybox devmem 0x0243d040 - Analyze output values to confirm correct configuration.

- Execute the following command to check register values:

-

Adjust Clock Configuration:

- Ensure that the clock signal is configured correctly for idle low state:

- Confirm SPI mode settings in your application match your hardware requirements.

- Ensure that the clock signal is configured correctly for idle low state:

-

Modify Register Settings:

- If necessary, write new values to registers to adjust configurations:

sudo busybox devmem 0x0243d040 w 0x404 sudo busybox devmem 0x0243d040

- If necessary, write new values to registers to adjust configurations:

-

Test with Different Hardware Configurations:

- Isolate the issue by testing with different SPI devices or configurations.

- If available, use another Jetson Orin Nano board to rule out hardware defects.

-

Firmware and Driver Updates:

- Ensure that you are using the latest firmware and driver versions compatible with JetPack SDK.

- Follow NVIDIA’s documentation for updating firmware if required.

-

Consult Documentation and Community Resources:

- Refer to NVIDIA’s Jetson Developer Kit User Guide for detailed instructions on setup and troubleshooting.

- Engage with community forums for additional insights and shared experiences from other users facing similar issues.

-

Best Practices for Future Prevention:

- Always back up configurations before making changes.

- Document all configuration changes made during troubleshooting for future reference.

-

Unresolved Aspects:

- Some users reported that they found solutions through forum discussions, indicating that community input can be valuable in resolving complex issues.

By following these steps, users should be able to diagnose and potentially resolve issues related to configuring SPI interfaces on their Nvidia Jetson Orin Nano Developer Kit effectively.