Auto Power-On Design for Nvidia Jetson Orin Nano Dev Board

Issue Overview

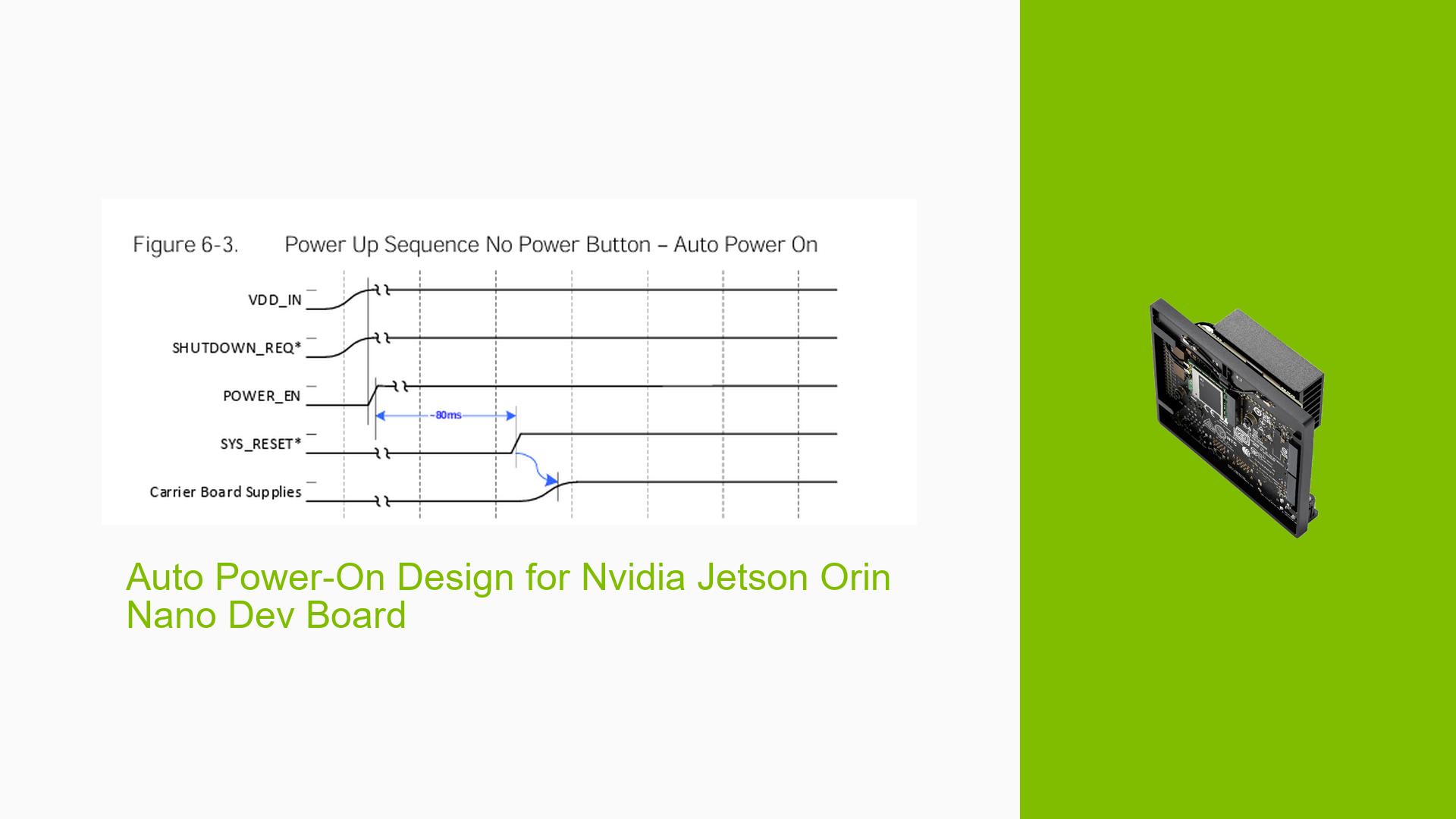

Users of the Nvidia Jetson Orin Nano Dev board are seeking a minimal design approach for products that do not require a power button. The main focus is on simplifying the power-on sequence, potentially reducing complexity and build costs. Specifically, users are interested in tying the POWER_EN signal directly to the VDD_IN supply and using the SYS_RESET output signal to enable carrier board supplies.

Possible Causes

-

Design Complexity: The standard power-on sequence may involve unnecessary components for products that don’t require manual power control.

-

Cost Considerations: The current design might include components that add to the build cost without providing necessary functionality for certain use cases.

-

Timing Constraints: The power-on sequence has specific timing requirements that need to be met for proper functionality, even in an auto-power-on scenario.

Troubleshooting Steps, Solutions & Fixes

Understanding the Auto Power-On Design

The auto power-on design for the Nvidia Jetson Orin Nano Dev board requires careful consideration of the power sequencing. Here are the key points and potential solutions:

-

POWER_EN Signal Timing:

- POWER_EN should be high after VDD_IN is stable.

- The timing requirement is approximately 80ms.

-

Reference Design:

- Refer to the Power ON/OFF Logic design of the P3449 schematic for an auto-power-on design example.

-

RC Circuit for Auto Power-On:

- The reference design uses a 412k resistor and a 2.2uF capacitor.

- This creates an RC combination with a time constant of approximately 0.9 seconds.

- The RC circuit ensures VDD_IN is stable before pulling POWER_EN high.

-

Simplified Design Approach:

- For products without a reset or power button, it may be possible to simplify the design.

- Consider tying the left side of the 412k resistor directly to VDD_IN.

-

Caution and Validation:

- While the simplified approach may work in theory, it has not been officially validated.

- Users should thoroughly test this configuration to ensure proper functionality and stability.

Implementation Steps

-

Review the P3449 schematic for the auto-power-on design reference.

-

Implement the RC circuit:

- Use a 412k resistor and a 2.2uF capacitor.

- Connect the capacitor between POWER_EN and ground.

- Connect the resistor between VDD_IN and POWER_EN.

-

For a potentially simplified design:

- Remove the reset and power button components if not needed.

- Connect the 412k resistor directly to VDD_IN.

-

Validate the design:

- Test the power-on sequence thoroughly.

- Ensure that POWER_EN goes high approximately 80ms after VDD_IN stabilizes.

- Monitor system stability and performance during and after power-on.

-

Consider power supply implications:

- Ensure that the carrier board supplies are properly enabled using the SYS_RESET output signal.

Best Practices

-

Always adhere to the timing requirements specified in the Jetson Orin Nano Dev board documentation.

-

Conduct extensive testing of any modified power-on designs to ensure reliability and stability.

-

Monitor temperature and power consumption during testing to verify that the simplified design doesn’t introduce any thermal or power issues.

-

Document any changes made to the standard design for future reference and troubleshooting.

-

Consider consulting with Nvidia support or experienced developers before implementing significant changes to the power-on design in production environments.