Issues with MIPI-CSI2 on Jetson Orin Nano Dev Board

Issue Overview

Users are experiencing difficulties capturing images using a custom MIPI-CSI2 driver on the Jetson Orin Nano Dev board. The specific symptoms include successful driver registration (evidenced by the creation of /dev/video0), but no image capture occurs when attempting to use the camera. This issue arises during the development of a driver for the ISL79987 video decoder, with the following system specifications:

- System on Module (SOM): Jetson Orin Nano

- Carrier Board: Custom Board

- Camera: Analog type (1 camera, with plans for 4)

- CSI Port Used: CSI 0

- JetPack Version: 5.1.1 (L4T: 35.3.1)

The problem appears to be consistent across attempts, significantly impacting user experience as it prevents any image processing or camera functionality from being realized.

Possible Causes

-

Device Tree Configuration Errors:

- The device tree (DT) file may not be correctly configured, leading to improper device initialization.

-

Polarity Issues:

- Polarity swap issues in the CSI lanes could prevent proper communication between the camera and the board.

-

Clock Configuration Problems:

- Insufficient clock speeds or misconfigured clock settings may hinder data transmission.

-

Driver Bugs:

- The backported driver from Linux 6.x to Linux 5.10 may contain bugs that affect functionality.

-

Environmental Factors:

- Issues such as power supply inconsistencies or thermal conditions could impact performance.

-

User Misconfigurations:

- Incorrect settings in the device tree or other configuration files may lead to failures in image capture.

Troubleshooting Steps, Solutions & Fixes

-

Verify Device Tree Configuration:

- Check the DT file for correctness, specifically focusing on:

num_csi_lanesshould match the number of active lanes.- Ensure correct endpoint configurations and bus widths are set.

- Check the DT file for correctness, specifically focusing on:

-

Adjust Polarity Settings:

- Modify the

lane_polarityproperty in the device tree based on your schematic:lane_polarity = "2"; // For CSI0 - If polarity swap is necessary, adjust accordingly (e.g.,

lane_polarity = "6";).

- Modify the

-

Boost Clock Rates:

- Execute commands to lock and boost clock rates for VI, CSI, ISP, and EMC:

sudo su echo 1 > /sys/kernel/debug/bpmp/debug/clk/vi/mrq_rate_locked echo 1 > /sys/kernel/debug/bpmp/debug/clk/isp/mrq_rate_locked echo 1 > /sys/kernel/debug/bpmp/debug/clk/nvcsi/mrq_rate_locked echo 1 > /sys/kernel/debug/bpmp/debug/clk/emc/mrq_rate_locked - Check maximum clock rates with:

cat /sys/kernel/debug/bpmp/debug/clk/vi/max_rate | tee /sys/kernel/debug/bpmp/debug/clk/vi/rate

- Execute commands to lock and boost clock rates for VI, CSI, ISP, and EMC:

-

Test with Different Configurations:

- Isolate issues by testing with different hardware setups or configurations.

- Consider using a different camera if available to rule out hardware defects.

-

Recompile Device Tree Binary:

- If changes are made to the DT file, recompile it:

dtc -I dts -O dtb -o output.dtb temp.dts - Update boot configurations in

/boot/extlinux/extlinux.confto load the new DTB file.

- If changes are made to the DT file, recompile it:

-

Investigate PHY Interrupts:

- Monitor for PHY interrupt errors indicating LP sequence issues; this could suggest problems on the camera side rather than on the board itself.

-

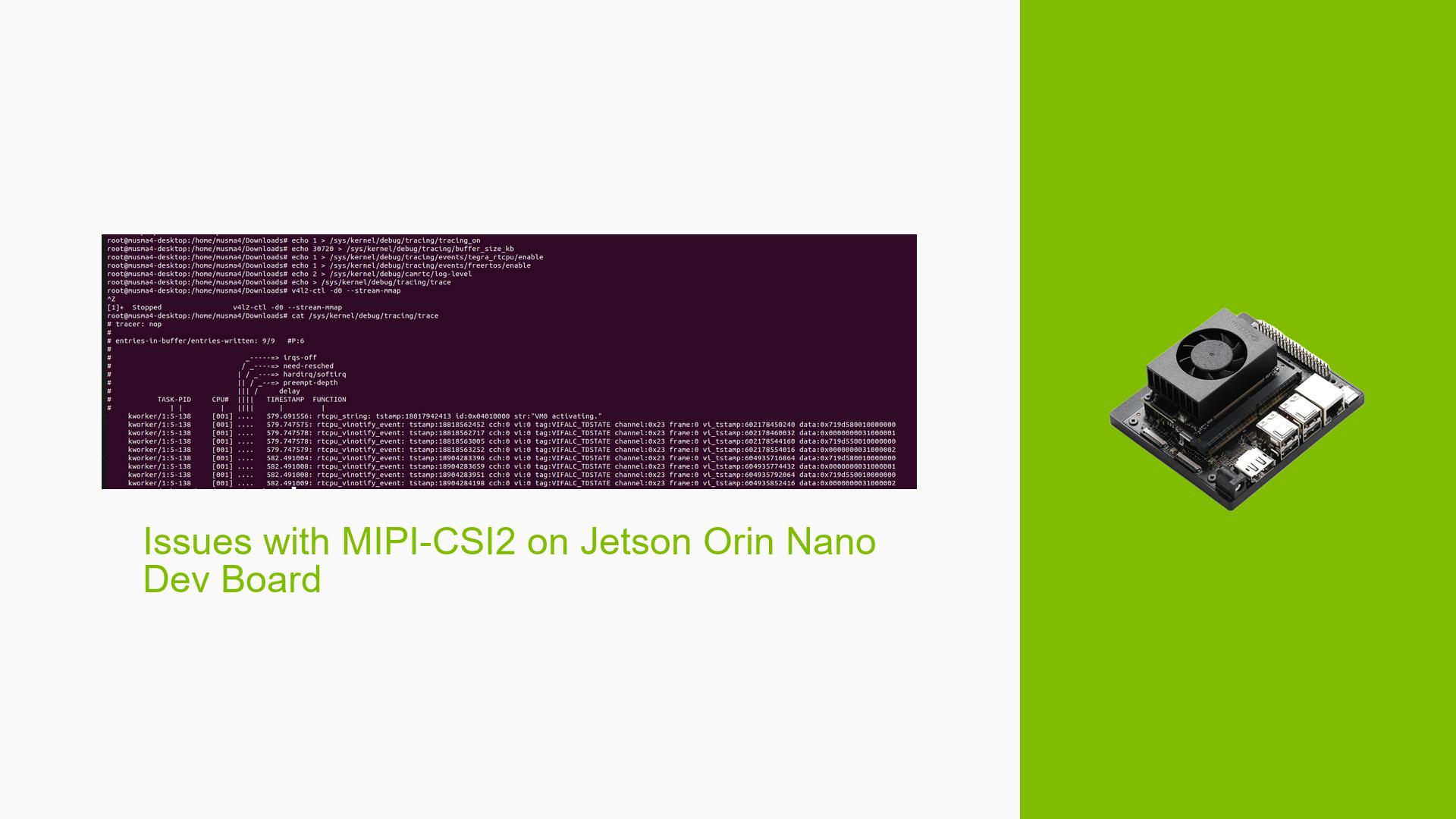

Review Debug Logs:

- Utilize logs from

dmesgand other debugging tools to identify any underlying issues during image capture attempts.

- Utilize logs from

-

Consult Documentation:

- Refer to NVIDIA’s developer guide for property-value pairs and other relevant documentation that might provide insights into configuration settings.

-

Community Feedback:

- Engage with community forums for shared experiences and solutions; many users have reported success by following similar troubleshooting steps.

By systematically addressing these areas, users can potentially resolve their image capture issues with the Jetson Orin Nano Dev board and enhance their development experience.