Jetson Orin Nano M2M GPIO Configuration Issue

Issue Overview

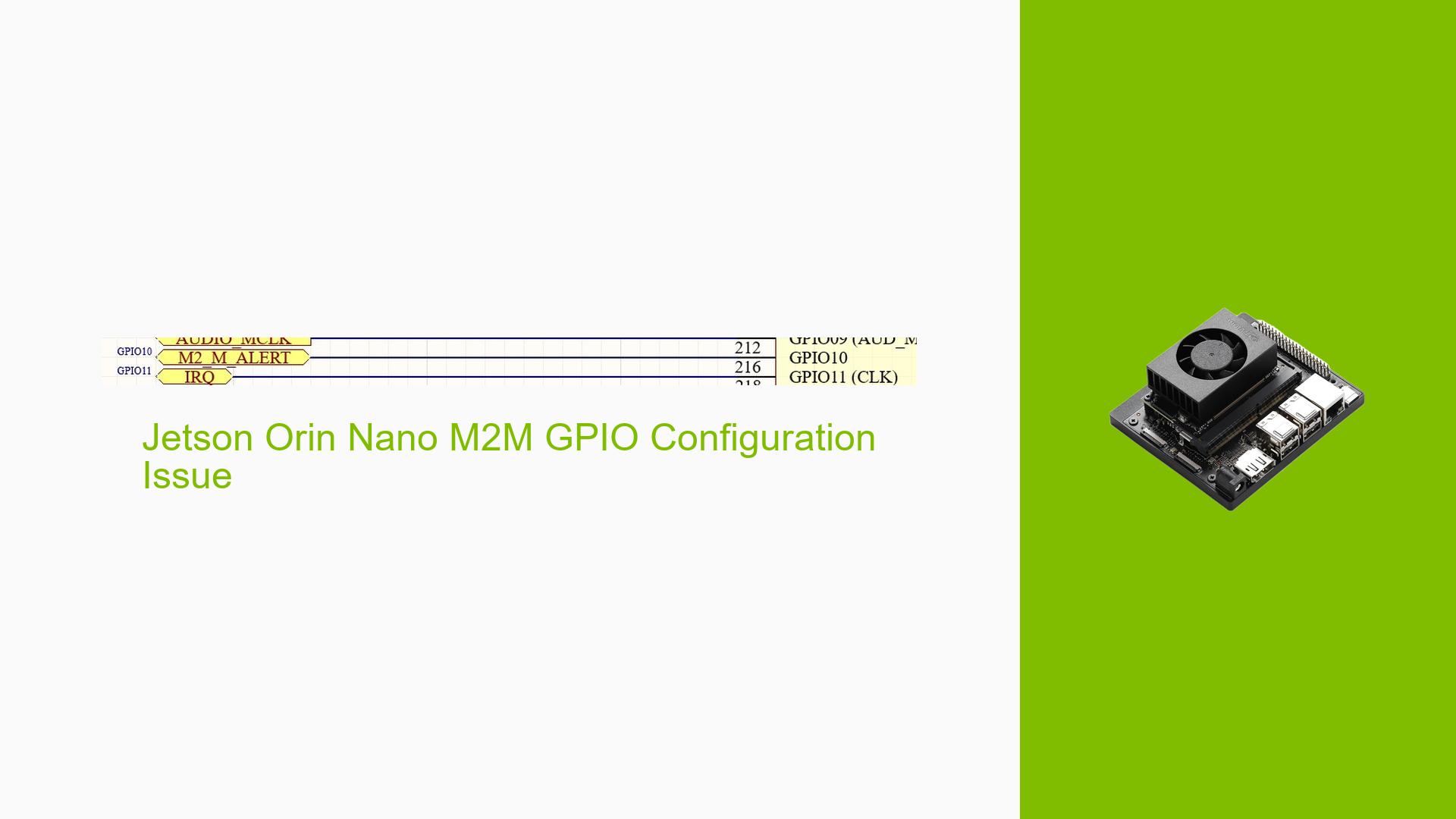

The discussion centers around the configuration of the Nvidia Jetson Orin Nano Dev board, specifically regarding the use of GPIO10 (pin 212) for an alert signal in an M2M (Machine to Machine) application. Users have reported confusion about the pin’s functionality and its configuration in the pinmux spreadsheet.

Symptoms and Context

- Users are unable to select M2.M ALERT on the pinmux spreadsheet for GPIO10.

- There is uncertainty regarding how to properly configure pin 212 for its intended use.

- The issue arises during the design phase of a carrier board for the Orin Nano, indicating a need for proper hardware setup.

Relevant Specifications

- The specific pin in question is GPIO10, also referred to as pin 212 on the Orin Nano Dev board.

- The configuration is crucial for applications requiring alert signals.

Frequency and Impact

- The issue appears to be common among users designing custom carriers, potentially affecting multiple projects.

- Misconfiguration could lead to failure in alert signal transmission, impacting system functionality and user experience.

Possible Causes

-

Hardware Incompatibilities or Defects: If there are defects in the hardware design or compatibility issues with other components, this could prevent proper functionality of GPIO10.

-

Software Bugs or Conflicts: The pinmux spreadsheet may contain bugs or outdated information that could lead to confusion about pin configurations.

-

Configuration Errors: Incorrect settings in the pinmux configuration could lead to GPIO10 not functioning as expected.

-

Driver Issues: Outdated or incorrect drivers may not support the intended use of GPIO10 for alert signals.

-

User Errors or Misconfigurations: Users may not be familiar with the correct setup procedures, leading to improper configurations.

Troubleshooting Steps, Solutions & Fixes

Step-by-Step Instructions

-

Verify Pin Functionality:

- Confirm that GPIO10 (pin 212) is indeed intended for M2.M ALERT by checking official documentation and community forums.

-

Check Pinmux Settings:

- Access the pinmux spreadsheet and ensure that GPIO10 is set correctly. For this specific case, it should be configured as

GPIO3_PEE.02.

- Access the pinmux spreadsheet and ensure that GPIO10 is set correctly. For this specific case, it should be configured as

-

Use Default Settings:

- As indicated by forum replies, keeping the default setting for GPIO10 as

GPIO3_PEE.02is recommended. This setting allows for proper wake function capabilities.

- As indicated by forum replies, keeping the default setting for GPIO10 as

-

Testing Configuration:

- After configuring GPIO10, test its functionality by running a simple script that toggles the GPIO state to confirm it responds as expected.

-

Consult Documentation:

- Refer to Nvidia’s official documentation for any updates or additional guidance on configuring GPIO pins on the Orin Nano Dev board.

Commands and Procedures

- To check and configure GPIO settings, you may use the following command in your terminal:

# Check current GPIO settings

cat /sys/class/gpio/gpio212/value

# Export GPIO if not already done

echo "212" > /sys/class/gpio/export

# Set direction

echo "out" > /sys/class/gpio/gpio212/direction

# Toggle GPIO value

echo "1" > /sys/class/gpio/gpio212/value

sleep 1

echo "0" > /sys/class/gpio/gpio212/value

Additional Recommendations

-

Firmware Updates: Ensure that your Jetson Orin Nano is running the latest firmware version to avoid any bugs related to GPIO handling.

-

Community Support: Engage with community forums for shared experiences and solutions from other users who may have faced similar issues.

Best Practices

-

Always refer to official documentation when configuring hardware components.

-

Keep your development environment updated with the latest software and drivers.

Unresolved Aspects

While users have successfully configured GPIO10 as GPIO3_PEE.02, further investigation may be needed into why M2.M ALERT cannot be selected in the pinmux spreadsheet. Additional insights from Nvidia’s technical support may clarify this limitation.